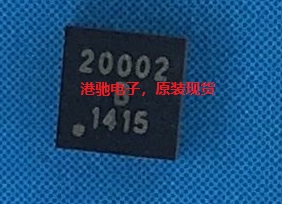

MC20002 METICOM 原厂全新原装

2019-08-24

MC20002 METICOM 原厂全新原装

MC20002 METICOM 原厂全新原装

MC 20002是一种高性能的FPGA桥芯片,它将输入的LVDS高速和输入的CMOS低速数据流转换为单通道MIPI D-PHY兼容的输出流。MC 20002还可以将LVDS信号转换为SLV信号。

MC 20002可以连接到任何信号源,例如FPGA或DSP。

在HS(高速)模式下,数据速率可以从0 Mbps到2.5Gbps,而在LPDT(低功率数据传输)模式下,数据速率可高达20 Mbps。

在MIPI D-PHY模式下THS-准备定时可由主机设备控制。

关键特征

输出符合使用dsi、csi-1和csi-2标准的mipi d-phy接口。

HS模式数据速率:最高2.5Gbps

LPDT模式数据速率:高达20 Mbps

柔性THS-准备MIPI D-PHY模式下的定时

LVDS输入到SLV输出的转换

LVDS数据速率:最高2.5Gbps

不需要额外的平移器

提供QFN-16包(VQFN-16-4)

3mm*3mm*0.9mm,0.5mm螺距

The MC20002 is a high performance FPGA bridge IC that converts incoming LVDS high speed and incoming CMOS low speed data streams into a single lane MIPI D-PHY compliant output stream. The MC20002 can also convert a LVDS signal into a SLVS signal.

The MC20002 can be connected to any signal source, for example FPGAs or DSPs.

Data rates can be from 0 Mbps to 2.5 Gbps in HS (High Speed) mode and up to 20 Mbps in LPDT (Low Power Data Transmission) mode.

In MIPI D-PHY mode the THS-PREPARE timing can be controlled by the host device.Key Features

Output is compliant to MIPI D-PHY interfaces using the DSI, CSI-1 and CSI-2 standards

HS mode data rate: up to a maximum of 2.5 Gbps

LPDT mode data rate: up to 20 Mbps

Flexible THS-PREPARE timing in MIPI D-PHY mode

Conversion of LVDS input to SLVS output

LVDS data rate: up to a maximum of 2.5 Gbps

No additional level shifters needed

Available as a QFN-16 package (VQFN-16-4)

3mm * 3mm * 0.9mm, 0.5mm pitch